Eines der schönen Dinge an Floating-Gate-Transistoren ist, wenn Sie sie in einem analogen Sinne verwenden, dass PVT nicht so wichtig ist, wie Sie tatsächlich mit dem Schwellenwert optimieren können, indem Sie Ladung auf dem Floating-Knoten hinzufügen oder entfernen span class = "math-container"> \ $ V_Q \ $ span>. Der einfachste Weg, ein Floating-Gate zu "simulieren", besteht darin, einfach eine Spannungsquelle an das Gate anzubringen, um einen effektiven Offset zu erzeugen.

Ich kann mir vorstellen, dass diese Papiere von Duffy, Hasler, Basu, Tor, stammen. und Krumenacher; Ich glaube jedoch nicht, dass ein Heißelektroneninjektionsmodell aufgrund von Stoßionisation (weshalb ich davon ausgehe, dass Sie einen pFET verwenden) in die Öffentlichkeit gelangt ist, aber ich halte mit diesen Kreisen nicht mehr Schritt. Kapitel 2 von Haslers Ph.D. Die Arbeit von Caltech unter Carver Mead gibt Ihnen die vollständige Modellierung für den nFET. Duffys Entwurf schwebt herum und er hat pFETs gemacht, aber meines Wissens hat er seine Arbeit nicht abgeschlossen. Die Quanteneffekte sind für das Tunneln sowohl für nFETs als auch für pFETs gleich. Die pFET-Physik für die Injektion ist jedoch unterschiedlich.

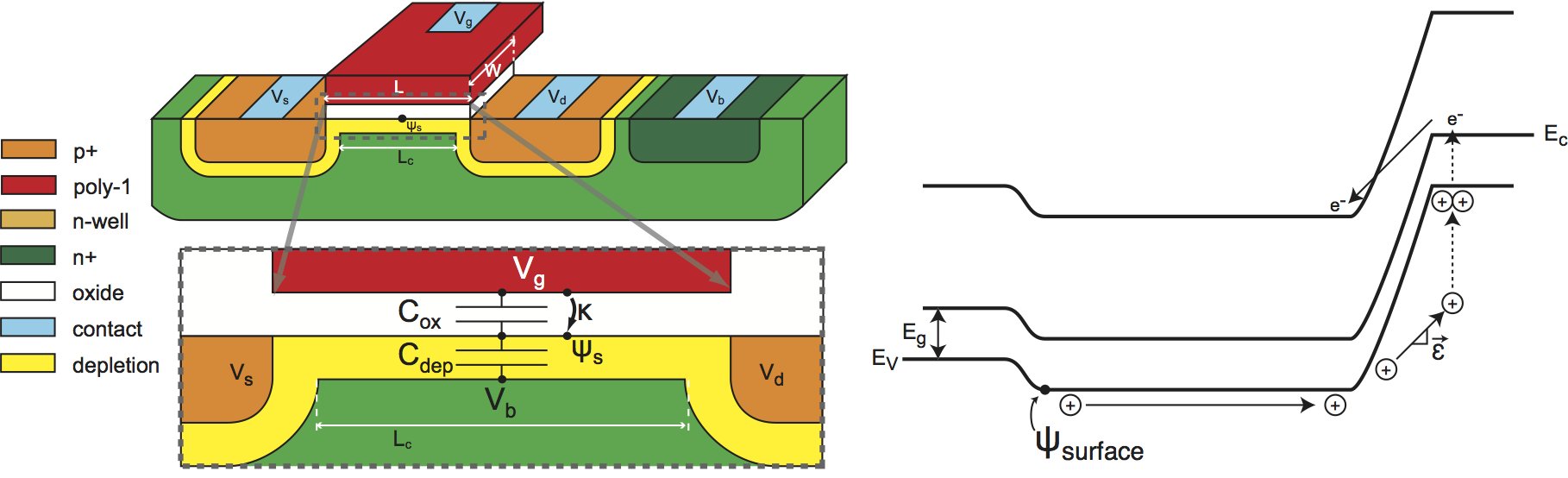

Hier ist eine visuelle Beschreibung des Prozesses aus meiner Arbeit. Sie können Haslers Arbeit modifizieren, indem Sie die Wahrscheinlichkeit einer Stoßionisation und dann die Gate-Bedingungen ermitteln, die erforderlich sind, um das Elektron zum Gate anzuziehen. Sie können eine spannungsgesteuerte Stromquelle mit einem idealen BJT verwenden, um eine gute logarithmische Steuerung zwischen Gate und Drain zu erhalten, da die Barriere \ $ \ Phi_ {DC} \ $ span> steuert, was Sie modellieren möchten.

Ich verwende hierfür das EKV -Modell, aber es ist nur aufgrund meiner Implementierung etwas schlampig. Ich berechne tatsächlich zurück, was für die FETs-Daten aus der EKV 2.6-Extraktion erforderlich ist, und erhalte dann das Doping, und Sie können von dort aus fortfahren.

BEARBEITEN: Basierend auf den Kommentaren, die Strom durch einen pFET in EKV ohne Drainabhängigkeit wäre

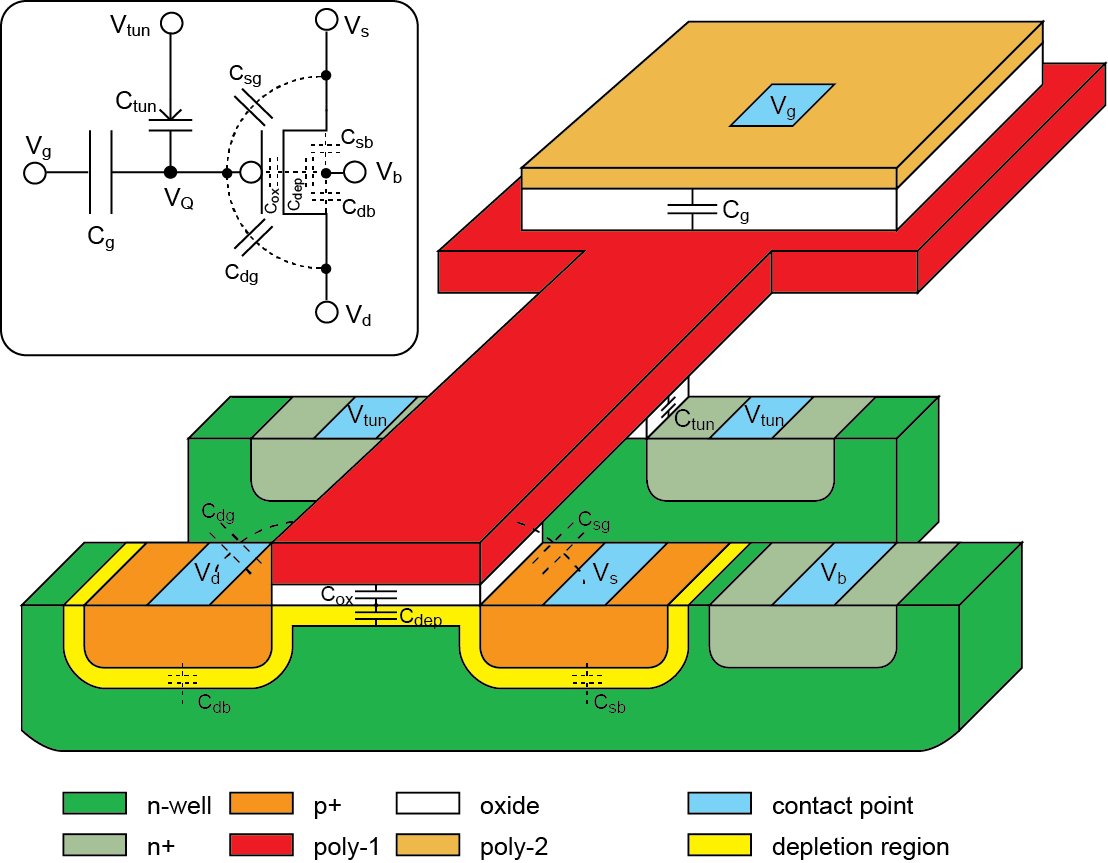

$$ I_ {f, r} = I_ {thp} \ ln ^ 2 \ left [1+ e ^ {\ left [{\ left (\ kappa \ left (V_b -V_g) + V_ {thp} \ rechts) \ rechts) - \ links (V_ {b} -V_ {s, d} \ rechts)} \ rechts] / \ links ({2 U_ {T}} \ rechts)} \ rechts ] $$ span> und dies gibt Ihnen eine Gleichung, in der das Oberflächenpotential \ $ \ kappa V_g \ $ span> ist, weil \ $ \ kappa \ $ span> ist der Kanalteiler. Dies ist es, was die Oberfläche steuert. Wenn Sie das Gerät "schweben" lassen, kommt es zu diesem kapazitiv gekoppelten Durcheinander:

Das Oberflächenpotential in Bezug auf den neuen "Gate" -Anschluss ist $$ V_ {fg} = {V_ {Q}} + \ frac {C_ {in}} {C_T} V_g + \ frac {C_ {tun}} {C_T} V_ {tun} + \ frac {C_ {gd}} {C_T} V_ {d} + \ frac {C_ {gs}} {C_T} V_ {s} + \ frac {C_ {ox}} {C_T} V_b $$ span> Wenn der schwebende Knoten "negativer" wird, verschiebt sich daher der Schwellenwert vom Standpunkt des Gate-Eingangs. Ich beziehe mich immer auf alles von der Oberfläche, wenn ich diese Geräte verwende, da Sie sich dann nicht um unterschiedliche Kondensatorgrößen und -verhalten kümmern müssen.