Dies ist eine ziemlich allgemeine Frage, und einige der anderen Antworten sind richtig. Aber ich möchte näher auf das eingehen, was hier wirklich vor sich geht. Nur für mehr Kontext.

Erstens müssen Sie vorsichtig sein, es gibt verschiedene Transistorkonstruktionen. In einem HexFET (der in Leistungsanwendungen verwendet wird und immer nur einzelne Transistoren in einem Gehäuse sind) verbindet der Prozess das S / D miteinander, die Struktur ist asymmetrisch und für hohen Strom optimiert. In einem IC-Prozess, der DMOS (Extended Drain - für Hochspannungsfestigkeit) verwendet, müssen Sie auch die Source an die Schiene binden.

Bei IC-Prozessen haben Sie jedoch beim Auslegen der Transistoren ein Gate Strukturen und S / D-Strukturen (wörtlich Source / Drain), da in einem idealen Prozess Source und Drain austauschbar sind.

Die Verbindung des Bulk definiert, welcher der beiden Terminals die Quelle ist.

-> Dies ist der entscheidende Punkt.

Wenn Sie beispielsweise einen SOI-Prozess (Silicon On Insulator) verwenden, der 4 Klemmen-Transistoren aufweist (nicht FD - vollständig erschöpft). Dann könnte man nur wirklich von den beiden Anschlüssen der Transistoren als S / Ds sprechen.

In Massenprozessen verwenden alle DSM-Prozesse (Deep Sub-Micron) Wafer vom P-Typ (viele Gründe dafür, Im Wesentlichen können jedoch Wafer vom P-Typ hergestellt werden (N-Typ sind härter). Das bedeutet, dass die P-Wanne für den NMOS-Transistor mit Masse verbunden ist, also ist die Masse. Selbst in diesem Fall wird die Quelle manchmal für einen gewünschten Effekt vom Boden ferngehalten. Dies erhöht die Quellenleckage, aber manchmal lohnt es sich.

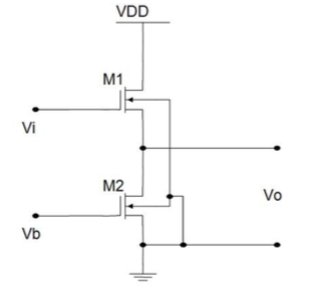

Der Nachteil dieser Struktur besteht darin, dass die Leistung der NMOS begrenzt ist. Schauen Sie sich einfach einen einfachen Source Follower an, der in PMOS und in NMOS implementiert ist (Bild von NMOS unten). In einer PMOS-Implementierung ist die NWell im Substrat (das vom p-Typ ist) in Sperrrichtung vorgespannt und kann schweben. Ein PMOS-Quellfolger kann bei ordnungsgemäßer Verdrahtung eine Verstärkung von 1,0 haben.

Betrachten eines NMOS-Quellenfolgers:

Bild aus (1) ausgeschnitten

Das untere Vb ist einfach eine Stromquelle für die Verstärkervorspannung und die aktive Last. Sie können sehen, dass bei M1 die Masse an den Boden gebunden ist. Das bedeutet, dass die Quelle von M1 schwebt und somit M1 unter dem Backgate-Effekt leidet. Das Nettoergebnis ist, dass dieser Verstärker höchstens eine Verstärkung von ~ 0,8X erreichen kann. In dieser Zeichnung würde die Verstärkung auf ~ 1,0X springen, wenn Sie den M1-Bulk ausschneiden und mit Vo verbinden würden.

Sie werden feststellen, dass andere erwähnt haben, dass Bulk und Source miteinander verbunden sind, um den Transistor zu optimieren . In Wirklichkeit gilt das nur für die Geräte auf der Schiene. Sie können sehen, dass jeder gestapelte Transistor diesen Back-Gate-Effekt in allen Transistoren außerhalb der Schiene manifestiert.

Dies ist jedoch ein enger Blick auf die Dinge. Wenn wir herumlaufen und einen schönen Prozess machen würden, bei dem das Backgate verfügbar wäre, hätten wir (zumindest) ein paar Probleme. Eine wäre, dass die zusätzliche Kapazität der Bohrloch-zu-Masse-Verbindung die Dinge verlangsamen würde. Die Bohrlochabstände müssten vergrößert werden, da die Bohrlöcher jetzt getrennt sind, sodass die Dichte sinken würde, und dann gibt es die Probleme zusätzlicher Verbindungen mit der Masse, die ebenfalls Platz beanspruchen. Zum größten Teil und insbesondere für digitale Geräte sind diese Effekte weitaus schlimmer.

(1) Shedge, M., & Itole, M. (2013). Analyse und Design von CMOS Source Followern und Super Source Followern. ACEEE Int J on….