Die Antworten in diesem Thread stimmen bisher alle darin überein, dass "es darauf ankommt". Ich dachte, es lohnt sich, den in einigen Antworten erwähnten Loop-Bereich zu erweitern, da dies hier der entscheidende Faktor ist.

Es geht um den Loop-Bereich, der von der Kappe und dem Chip gebildet wird. Am besten verstehen Sie, was Schleifenbereich ist, dann können Sie den besten Kompromiss für jede Situation auswählen. Ich fürchte, es gibt keine "Mach es einfach so, immer" -Lösung.

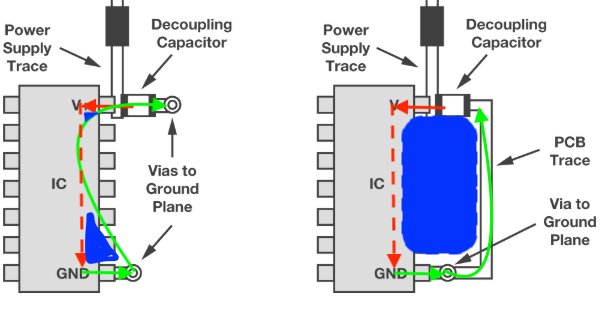

Die Schleifenfläche ist die Fläche, die durch den Pfad des von der Kappe in den Chip fließenden Stroms und den Pfad des aus dem Chip zurück zur Kappe fließenden Stroms gebildet wird. Nennen wir den In-Pfad V + und den Rückweg GND.

Für die meisten praktischen Zwecke bis zu 1-GHz-Frequenzen können Sie sich einfach den Bereich der oberen Abwärtsschleife ansehen (d. h. ihn einfach über Ihre Bilder zeichnen). Bei höheren Frequenzen müssen Sie es möglicherweise in 3D betrachten.

Wenn Sie die Ströme zwingen, in Spuren zu fließen, ist der Pfad frei - es sind die Linien der Spuren. Wenn Sie zulassen, dass ein Strom in einer Ebene fließt und der andere in Spuren verläuft, folgt der Pfad der höherfrequenten Ströme in der Ebene nicht dem kürzesten Pfad (den Sie möglicherweise erwarten) - stattdessen versuchen sie, dem Pfad des zu folgen Strom auf Spuren beschränkt. Die niedrigere Frequenz oder der niedrigere Gleichstrom in der Ebene fließt direkt zur Versorgung und lässt den Entkoppler vollständig aus, aber diese sind im Zusammenhang mit der Platzierung des Entkopplers nicht interessant.

Ich habe Ihr Bild jeweils mit dem Loop-Bereich (Draufsicht) versehen.

Die roten durchgezogenen Linien sind V + -Flüsse von der Kappe zum Chip. & Die rot gepunktete Linie ist der interne Stromfluss durch den Chip.

Die grünen Linien sind GND-Flüsse vom Chip zur Kappe. Beachten Sie für das Bild auf der linken Seite, dass der tatsächliche Pfad, den die grüne Linie von Via nach Via nimmt, von der Frequenz abhängt. Je höher die Frequenz, desto extremer ist die Abweichung vom kürzesten Pfad, wenn der Rückstrom versucht, dem Vorwärtsstrom zu folgen.

Die blauen Bereiche sind Schleifenbereiche.Sie können sehen, welches besser ist - es ist das mit dem geringsten Blau.

Hinweis Ich habe den richtigen / falschen Text ausgeschnitten - es hängt ganz von der Anwendung ab, ob dies wahr ist oder nicht - für bestimmte Anwendungen ist die rechte Lösung möglicherweise gut genug und bietet möglicherweise andere Routing-Vorteile.Es ist jedoch unwahrscheinlich, dass dies die beste Lösung ist.

Ich hoffe das hilft.